Recently, TSMC officially disclosed the details of its latest 3nm process. Its transistor density creates a new record, 250 million / mm². For reference, the Kirin 990 5G with TSMC's 7nm EUV process has a size of 113.31mm², a transistor density of 10.3 billion, an average of 90 million / mm². However, the 3nm process transistor density is 3.6 times that of the 7nm process. This density is visually analogized to reducing the Pentium 4 processor to the size of the needle.

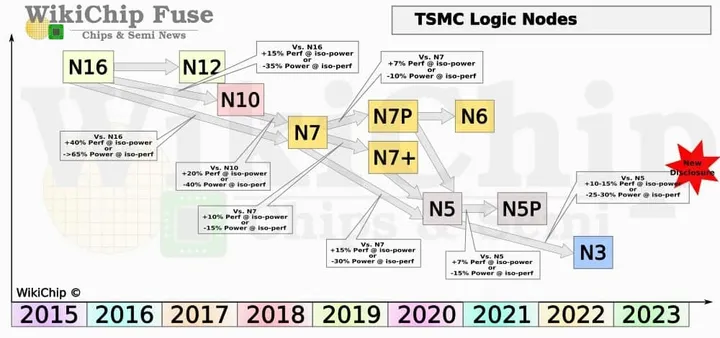

In terms of performance improvement, TSMC's 5nm performance is 10% - 15% higher than 7nm, and the energy consumption reduces by 25% - 30%. However, the 3nm performance is 5% higher than 5nm and energy consumption increased by 15%.

In terms of density, TSMC says the 3nm has a 1.7x density improvement over the 5nm process. According to WikiChip, 3nm should offer a cell-level density of just under 300 million transistors per millimeter square.

In addition, TSMC said that the 3nm process development is in line with its original schedule. According to TSMC CEO, CC Wei, it will commence risk trial production in 2021. The mass production will commence in the second half of 2022.

In terms of technology, TSMC evaluates various options and believes that the current FinFET process is better in terms of cost and energy efficiency. Thus, the first set of 3nm chips will still use FinFET transistor technology. However, Samsung, an old rival of TSMC, is betting on the 3nm node to turn over, thus its progress and technology choices are very radical. It will eliminate the FinFET transistors and directly use GAA to surround the gate transistors.

Popular News

Latest News

Loading